- Stack Overflow for Teams Where developers & technologists share private knowledge with coworkers

- Advertising & Talent Reach devs & technologists worldwide about your product, service or employer brand

- OverflowAI GenAI features for Teams

- OverflowAPI Train & fine-tune LLMs

- Labs The future of collective knowledge sharing

- About the company Visit the blog

Collectives™ on Stack Overflow

Find centralized, trusted content and collaborate around the technologies you use most.

Q&A for work

Connect and share knowledge within a single location that is structured and easy to search.

Get early access and see previews of new features.

Staging Ground badges

Earn badges by improving or asking questions in Staging Ground.

Bidirectional databus design

I need to communicate with a chip via a bidirectional databus (ULPI).

As far as I can ascertain, data is shifted out on the ULPI bus on rising clock edges, and read on falling clock edges. My problem is that when reading a register, I first need to be sensitive to rising edges (to write the command to the chip on the databus), and then to falling edges when reading register output onto the bus from the chip.

I'm unclear as to how to design this the best way.

I tried with one process which had a case statement, but for this to work, my process needs to be sensitive to both rising and falling edges, which I think is not good. Or is it actually OK?

2 Answers 2

A bidirectional bus is typically implemented by using a tristate buffer. When the tristate buffer output is "Z" you can read from the inout port, when the buffer is driving the line, it acts as an output. In VHDL, this can be implemented by directly instanciating a primitive (e.g. IOBUF for Xilinx device), or by letting your synthesis tool infer tristate buffer by describing logic as described above.

There are 3 signals you are dealing with here:

- T which is your tristate control. This signal will be derived from your synchronization logic, knowing the protocol of ULPI. That is since the bus is shared, there must be some way of knowing when you should be receiving data vs. sending data.

- I this is your input data that you wish to send across the bus, after being registered by the appropriate clock.

- O this is your output data that you are receiving over the bus, prior to any registering/synchronization.

Key: A tristate buffer is not synchronous. It is what you do before/after the tristate buffer that will properly synchronize your signal. In this case, you must synchronize your inputs to the tristate buffer (to be transmitted) on the rising clock edge, and registered data received from tristate buffer/IOBUF on the falling clock edge.

Sample Design.

Be mindful of cross clock domain crossings. There are many possible crossings here for data going out and coming from the bus, especially if your internal logic is driven on a different clock than the bus clock. I can't make a suggestion without more detail.

If you would like a behavioral representation of the tristate buffer to be inferred by the synthesis tools, can you could do something like this, instead of using unisim library and IOBUF :

I know that this is an very old article but my comment is for people who want to connect/implement ULPI. In ULPI there is no tristate data buffer. Read the chapter 2.3.1 Bus Ownership from "ULPI Interface Specification", if you want to know how transfer/transmit in ULPI must be implemented.

If you write the vhdl in the accepted answer your code wouldn't work all of the time. Some things which you must be care of are:

- turn around cycle

- aborting data

Your Answer

Reminder: Answers generated by artificial intelligence tools are not allowed on Stack Overflow. Learn more

Sign up or log in

Post as a guest.

Required, but never shown

By clicking “Post Your Answer”, you agree to our terms of service and acknowledge you have read our privacy policy .

Not the answer you're looking for? Browse other questions tagged vhdl or ask your own question .

- The Overflow Blog

- Brain Drain: David vs Goliath

- How API security is evolving for the GenAI era

- Featured on Meta

- Upcoming initiatives on Stack Overflow and across the Stack Exchange network...

- Site maintenance - Wednesday, October 23, 2024, 9:00 PM-10:00 PM EDT...

- Proposed designs to update the homepage for logged-in users

Hot Network Questions

- Why are political donations public?

- L'chatchila Ariber: what does it mean and where does it come from?

- (How) can I use a color as an adverb?

- How to translate the term "baby" as in "burn, baby, burn?"

- What happens between travelling and rest?

- Is it a coincidence that the smallest bit of action that fits into the universe is close to Planck's constant?

- Does it matter who I dispatch for gathering?

- What is the logical fallacy that goes like « If this person were X, then event Y would not have happened »

- How to download a file using a web link

- Rule based tikz picture

- Passport picture with hair but I’m bald now

- how do I keep my tremolo strat in tune?

- Problem with definition of tangent vectors as derivations

- What is the maximum proficiency level for fighting skills?

- Draw the Flag of Greenland

- A bird that is about as UNBIRD-LIKE as it is possible for a bird to be. | Is "unbird-like" applicable to other nouns?

- My players think there is a plot where there isn't one - should I create one?

- Obscure 1990s Fantasy book series about a male barbarian class warrior who can use shaman magic?

- Grimm's Law and PIE in general

- Meeting on a grid

- Why is it OK to cancel out terms when solving partial fractions?

- Fixing damage to my department due to nepotistic exec

- How is it possible for the eval to reduce after playing the best move?

- Is it possible that mosquitoes have been laying eggs and reproducing inside my house?

- Search forums

assigning delays for bidirectional signals

- Thread starter Tom

- Start date Aug 2, 2005

- Aug 2, 2005

Everyone, I've got a 'black box' component which has in, out and inout ports. This component is an existing design of a chip which cannot (should not) be modified. The VHDL model of this chip does not include any delays (in simulations all signals change immediately after the clock edge). For system-level simulations, I am building a wrapping entity around this 'black box' chip in which I model the delays on the output signals. This goes as follows: * input signals are assigned directly: input_signal_internal <= input_signal_external; * for output signals the real chip's delay is added: output_signal_external <= output_signal_internal after <whatever> ns; But what do I do for bidirectional signals ? Does a similar setup like for output signals work? Note that I do not have a simple handshake signal which tells me whether the bidirectional line is an input or an output at any specific time, but if needed I can probably infer the direction by decoding a bunch of external signals. Any suggestions? Is this possible without a direction signal? greetings, Tom

Ralf Hildebrandt

Tom said: I've got a 'black box' component which has in, out and inout ports. This component is an existing design of a chip which cannot (should not) be modified. The VHDL model of this chip does not include any delays (in simulations all signals change immediately after the clock edge). For system-level simulations, I am building a wrapping entity around this 'black box' chip in which I model the delays on the output signals. Click to expand...

- Aug 3, 2005

What about just synthesizing the "black box-component"? Then you get reliable delay estimations without manual interference. Click to expand...

Ok - the simulation time simulationg with the synthesized netlist and maybe additionally an sdf-file will be slower than behvioral simulation. Is this the reason, why you do not want to go this way? Click to expand...

One way, if you really have to model the delays is to split a bidirectional bus into two busses for each direction. Then you may insert delay elements for simulation for each bus. After all you may merge the two busses. Click to expand...

One more question: Why do you have bidirectional busses for on-chip-communication? Would't it be better to model this with two busses - one for each direction and use bidirectional busses only for pin I/O? Click to expand...

(not yet tested), which I found on http://groups.google.be/group/comp.lang.vhdl/browse_frm/thread/de067db014e088d7/7d14832588a0cabb -- bidirectional signal assignments with delays DBUS_link: for i in DBUS_ext'range generate DBUSi_link: ZeroOhm generic map (a_to_b_loss => 0 ns, b_to_a_loss => 1.234 ns) port map (A => DBUS_ext(i), B => DBUS_int(i)); end generate; Click to expand...

Tom said: Like I said I cannot change anything about the 'black box' component. This has bidirectional buses on its pin I/O's. Click to expand...

I think I may have found a solution in Ben Cohen's ZeroOhm component (not yet tested), which I found on http://groups.google.be/group/comp.lang.vhdl/browse_frm/thread/de067db014e088d7/7d14832588a0cabb Click to expand...

Ask a Question

Want to reply to this thread or ask your own question?

You'll need to choose a username for the site, which only take a couple of moments. After that, you can post your question and our members will help you out.

Similar Threads

| 1 | ||

| 4 | ||

| 1 | ||

| 5 | ||

| 0 | ||

| 0 | ||

| 1 | ||

| 3 |

Members online

Forum statistics, latest threads.

- Started by bobkuspe

- Today at 1:27 AM

- Started by bobbyking876

- Yesterday at 6:07 PM

- Started by Johnny97

- Yesterday at 8:22 AM

- Started by new_ojitomagico

- Friday at 4:00 AM

- Started by franklinshaw

- Thursday at 6:18 AM

- Started by cakexifx

- Wednesday at 10:57 PM

- Wednesday at 10:53 PM

- Started by Ondrej_frajer

- Wednesday at 9:52 PM

- Started by strawbs

- Wednesday at 11:52 AM

- Wednesday at 11:48 AM

Success! Subscription added.

Success! Subscription removed.

Sorry, you must verify to complete this action. Please click the verification link in your email. You may re-send via your profile .

- Intel Community

- Product Support Forums

- Intel® Quartus® Prime Software

Description of bidirectional signals and differential input signals in VHDL

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Printer Friendly Page

- Mark as New

- Report Inappropriate Content

View solution in original post

- All forum topics

- Previous topic

Link Copied

Community support is provided Monday to Friday. Other contact methods are available here .

Intel does not verify all solutions, including but not limited to any file transfers that may appear in this community. Accordingly, Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

For more complete information about compiler optimizations, see our Optimization Notice .

- ©Intel Corporation

- Terms of Use

- *Trademarks

- Supply Chain Transparency

Selected Signal Assignment

- Architecture

Reference Manual

- Section 9.5.2

Rules and Examples

The rules are the same as for the case statement , i.e. all possible choices must be included unless the others clause is used as the last choice:

A range or a selection may be specified as a choice:

As with the case statement, choices may not overlap:

As with the case statement, there is no implied priority to the choices:

The expressions assigned may be delayed. Transport delay mode may also be specified.

Any signal assignment may have an optional label.

The unaffected keyword indicates a choice where the signal is not given a new assignment. This is roughly equivalent to the use of the null statement within case:

The keywords inertial and reject may also be used in a selected signal assignment.

A selected signal assignment can be specified to run as a postponed process .

Synthesis Issues

Selected signal assignments are generally synthesizable.

A selected signal assignment will usually result in combinational logic being generated. Assignments to ‘Z’ will normally generate tri-state drivers. Assignment to ‘X’ may not be supported.

If a signal is conditionally assigned to itself, latches may be inferred.

Stack Exchange Network

Stack Exchange network consists of 183 Q&A communities including Stack Overflow , the largest, most trusted online community for developers to learn, share their knowledge, and build their careers.

Q&A for work

Connect and share knowledge within a single location that is structured and easy to search.

Signal assignment type

What is the meaning of "combinational assignment" and "registered assignment" to signals? In particular what are the differences between these two types of assignments?

- state-machines

2 Answers 2

Essentially, the difference boils down to whether the signal gets assigned on a clock edge or not.

Combinational code, like A <= B + 1 would have A being assigned B+1 "immediately," whereas

would result in A being assigned B+1 only on a rising clock edge. With code like this, other blocks can use the value of A being guaranteed that its value will be stable and unchanging after a clock edge.

Registers, or clock gating in general I suppose, are really what make designs of any complication possible. You create a pipeline of operations by putting a register at the border between operations. For example, the input operands to an ALU must be stable - in a register- so that the ALU can execute properly, and the result of the ALU's execution should be in a register so that whatever block uses it does not 'see' the changing values inside the ALU as the calculations take place, but only the stable last result.

- \$\begingroup\$ Question: Is a transparent latch considered combinatorial or registered? \$\endgroup\$ – The Photon Commented May 14, 2012 at 4:52

- \$\begingroup\$ Yes and no - the input to a transparent latch propagates directly to the output, not on a clock edge. But the addition of an enable signal could make the latch be controlled on a clock edge, ie, opaque. \$\endgroup\$ – Kevin H Commented May 14, 2012 at 16:17

Assignments in VHDL are neighter specified as registered or combinatorial. In VHDL the actual assignment type (the type of RTL logic generated) is just inferred.

Registers in VHDL are created explicitly by assigning a signal on a clock edge, though just because a process has a clock it does not mean all signals in that block will be assigned on every edge.

Also registers can be inferred without a clock, if some path through a process does not assign a signal, then VHDL assumes you meant to latch that signal between successive passes. This is called an inferred latch (and should be avoided).

VHDL does not know about the technology that you are going to be using. It does not know whether your synthisis engine can generate T,D,JK,SR, or any other sort of latch. For that reason it just suggests a latch, it is up to the synthisis enging to decide which latch fits the bill or if it is simply impossible. Similarlay the fitter might say that a particular latch requested by the synthisis enging is not available or there are no enough of them.

Your Answer

Sign up or log in, post as a guest.

Required, but never shown

By clicking “Post Your Answer”, you agree to our terms of service and acknowledge you have read our privacy policy .

Not the answer you're looking for? Browse other questions tagged vhdl signal state-machines or ask your own question .

- The Overflow Blog

- Brain Drain: David vs Goliath

- How API security is evolving for the GenAI era

- Featured on Meta

- Upcoming initiatives on Stack Overflow and across the Stack Exchange network...

- Site maintenance - Wednesday, October 23, 2024, 9:00 PM-10:00 PM EDT...

Hot Network Questions

- How can I find intersection of four sphere without solving the system of equations?

- Is it possible that mosquitoes have been laying eggs and reproducing inside my house?

- Draw the Flag of Greenland

- Did the U.S. government require SpaceX to study the impact of rocket launches on sharks and whales?

- How to replace a random string in an HTML table?

- Dance of The Knights puzzle

- Voltage divider with MOSFET to save power

- Problem with definition of tangent vectors as derivations

- Is it legal to say "the University welcomes applications from all individuals who self-declare as a woman" in job post?

- Obscure 1990s Fantasy book series about a male barbarian class warrior who can use shaman magic?

- What Exactly was The Baptist Saying?

- Taking damage while dying in 3.5

- ISS Cupola window coatings

- How would an ancient Chinese necromancer keep his skeletons burning?

- Why does the Gaza Strip use Israeli currency?

- Package tikz: Giving up on this path. Did you forget a semicolon?

- Why is it OK to cancel out terms when solving partial fractions?

- Fixing damage to my department due to nepotistic exec

- Grimm's Law and PIE in general

- What is the maximum proficiency level for fighting skills?

- Which generation of hard drives no longer required you to park the heads?

- How to cut wooden beam into 4 parts that can be reassembled into a cube?

- Can the four free GRE subject scores be stopped if the score is bad?

- Path Analysis with a variable use d as grouping variable and predictor at the same time

- Network Sites:

- Technical Articles

- Market Insights

- Or sign in with

- iHeartRadio

Concurrent Conditional and Selected Signal Assignment in VHDL

Join our engineering community sign-in with:.

This article will review the concurrent signal assignment statements in VHDL.

This article will first review the concept of concurrency in hardware description languages. Then, it will discuss two concurrent signal assignment statements in VHDL: the selected signal assignment and the conditional signal assignment. After giving some examples, we will briefly compare these two types of signal assignment statements.

Please see my article introducing the concept of VHDL if you're not familiar with it.

Concurrent vs. Sequential Statements

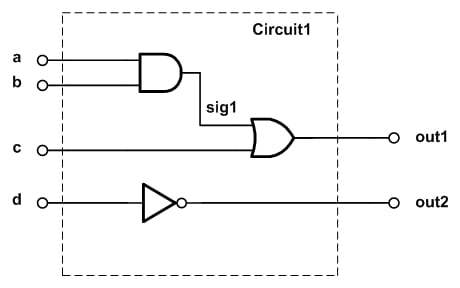

To understand the difference between the concurrent statements and the sequential ones, let’s consider a simple combinational circuit as shown in Figure 1.

Figure 1. A combinational circuit.

If we consider the operation of the three logic gates of this figure, we observe that each gate processes its current input(s) in an independent manner from other gates. These physical components are operating simultaneously. The moment they are powered, they will “concurrently” fulfill their functionality. Note that while, in practice, the AND gate has a delay to produce a valid output, this does not mean that the OR gate will stop its functionality and wait until the output of the AND gate is produced. The OR gate will function all the time; however, its output will not be valid until its inputs have settled.

Now, let’s examine the VHDL description of Figure 1. This is shown below:

The main part that we are here interested in is the definition of the three gates:

Each of these lines describes a physical component in Figure 1. For example, the second line, which describes the OR gate, takes sig1 and c as inputs and produces the OR of these two values. We saw that the physical components of Figure 1 operate concurrently. Hence, it is reasonable to expect that the VHDL description of these gates should be evaluated in a concurrent manner. In other words, the above three lines of the code are executed at the same time and there is no significance to the order of these statements. As a result, we can rewrite the architecture section of the above code as below:

Since these statements are evaluated at the same time, we call them concurrent statements. This type of code is quite different from what we have learned in basic computer programming where the lines of code are executed one after the other. For example, consider the following MATLAB code:

This code produces out1=1 and out2=1 . However, if we change the order of the statements to the following, the program will stop working because we are trying to use sig1 before it is generated.

While the VHDL code describing Figure 1 was executed concurrently, the above MATLAB code is evaluated sequentially (i.e., one line after the other). VHDL supports both the concurrent statements and the sequential ones. It's clear that the concurrent VHDL statements will allow us to easily describe a circuit such as the one in Figure 1 above. In a future article, we'll see that the sequential VHDL statements allow us to have a safer description of sequential circuits. Furthermore, using the sequential VHDL, we can easily describe a digital circuit in a behavioral manner. This capability can significantly facilitate digital hardware design.

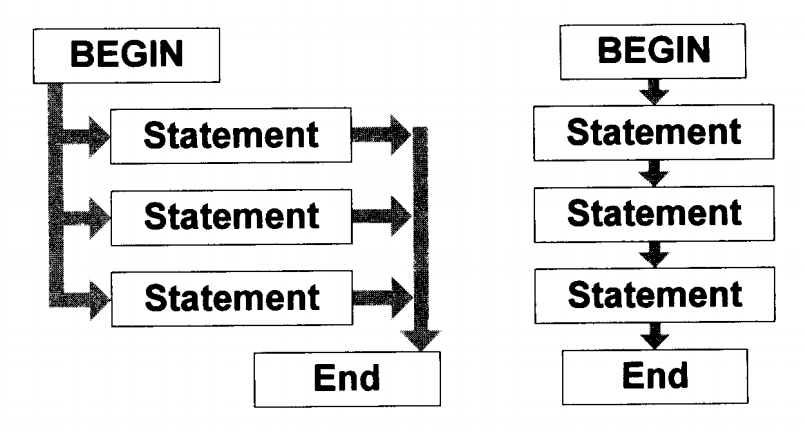

The following figure illustrates the difference between concurrent and sequential statements.

Figure 2. The difference between concurrent and sequential statements. Image courtesy of VHDL Made Easy .

Now let's take a look at two concurrent signal assignment statements in VHDL: “the selected signal assignment statement” and “the conditional signal assignment statement”.

Selected Signal Assignment or the “With/Select” Statement

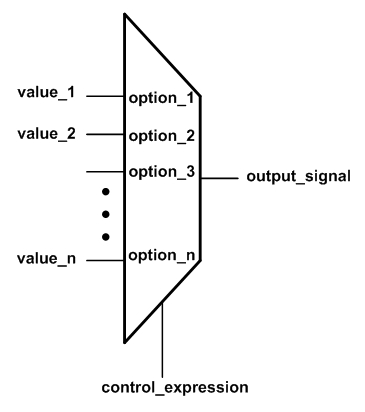

Consider an n -to-one multiplexer as shown in Figure 3. This block should choose one out of its n inputs and transfer the value of this input to the output terminal, i.e., output_signal .

Figure 3. A multiplexer selects one of its n inputs based on the value of the control_expression.

The selected signal assignment allows us to implement the functionality of a multiplexer. For example, the VHDL code describing the multiplexer of Figure 3 will be

Here, the value of the control_expression will be compared with the n possible options, i.e., option_1 , option_2 , …, option_n . When a match is found, the value corresponding to that particular option will be assigned to the output signal, i.e., output_signal . For example, if control_expression is the same as option_2 , then value_2 will be assigned to the output_signal .

Note that the options of a “with/select” assignment must be mutually exclusive, i.e., one option cannot be used more than once. Moreover, all the possible values of the control_expression must be included in the set of the options. The following example clarifies these points.

Example 1 : Use the "with/select" statement to describe a one-bit 4-to-1 multiplexer. Assume that the inputs to be selected are a , b , c , and d . And, a two-bit signal, sel , is used to choose the desired input and assign it to out1 .

The code for this multiplexer is given below:

Note that since the std_logic data type can take values other than “0” and “1” , the last line of the “with/select” statement needs to use the keyword “ others ” to take all the possible values of sel into account.

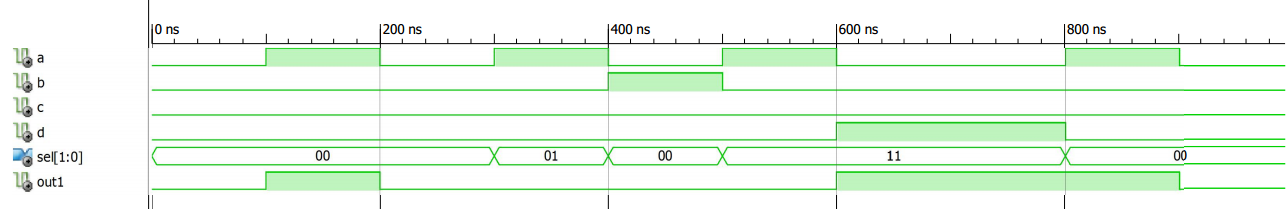

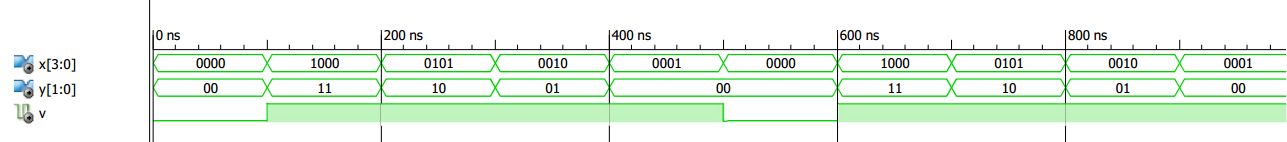

The following figure shows the simulation of this code using the Xilinx ISE simulator. (In case you’re not familiar with ISE, see this tutorial .) As shown in this figure, from 0 nanosecond (ns) until 300 ns the select input, sel , is 00, and, hence, out1 follows the input a . Similarly, you can verify the intended operation for the rest of the simulation interval.

Figure 4. The ISE simulation for the multiplexer of Example 1.

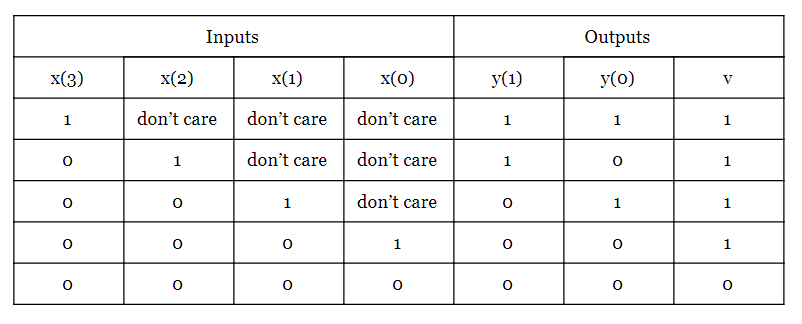

Example 2 : Use the “with/select” statement to describe a 4-to-2 priority encoder with the truth table shown below.

The following VHDL code can be used to describe the above truth table:

The ISE simulation is shown in Figure 5.

Figure 5. The ISE simulation for the priority encoder of Example 2.

Conditional signal assignment or the “when/else” statement.

The “when/else” statement is another way to describe the concurrent signal assignments similar to those in Examples 1 and 2. Since the syntax of this type of signal assignment is quite descriptive, let’s first see the VHDL code of a one-bit 4-to-1 multiplexer using the “when/else” statement and then discuss some details.

Example 3 : Use the when/else statement to describe a one-bit 4-to-1 multiplexer. Assume that the inputs to be selected are a , b , c , and d . And, a two-bit signal, sel , is used to choose the desired input and assign it to out1 .

The code will be

In this case, the expressions after “when” are evaluated successively until a true expression is found. The assignment corresponding to this true expression will be performed. If none of these expressions are true, the last assignment will be executed. In general, the syntax of the “when/else” statement will be:

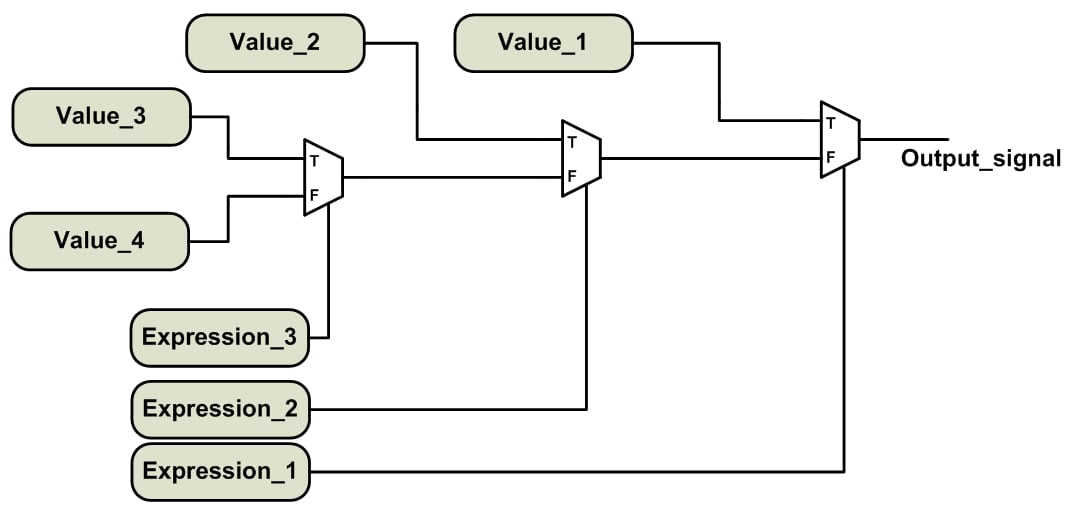

We should emphasize that the expressions after the “when” clauses are evaluated successively. As a result, the expressions evaluated earlier has a higher priority compared to the next ones. Considering this, we can obtain the conceptual diagram of this assignment as shown in Figure 6. This figure illustrates a conditional signal assignment with three “when” clauses.

Figure 6. The conceptual implementation of a “when/else” statement with three “when” clauses.

Let’s review the main features of the selected signal assignment and the conditional signal assignment.

“With/Select” vs. “When/Else” Assignment

As mentioned above, the options of a “with/select” assignment must be mutually exclusive, i.e., one option cannot be used more than once. Moreover, all the possible values of the control_expression must be included in the set of options. While the “with/select” assignment has a common controlling expression, a “when/else” assignment can operate on expressions with different arguments. For example, consider the following lines of code:

In this case, the expressions are evaluating two different signals, i.e., reset1 and clk .

For the “when/else” assignment, we may or may not include all the possible values of the expressions to be evaluated. For example, the multiplexer of Example 3 covers all the possible values of sel ; however, the above code does not. The above code implies that out1 should retain its previous value when none of the expressions are true. This causes the inference of a latch in the synthesized circuit.

Another important difference between the “with/select” and “when/else” assignment can be seen by comparing the conceptual implementation of these two statements. The priority network of Figure 6 involves a cascade of several logic gates. However, the “with/select” assignment avoids this chain structure and has a balanced structure. As a result, in theory, the “with/select” statement may have better performance in terms of the delay and area (see RTL Hardware Design Using VHDL: Coding for Efficiency, Portability, and Scalability , Xilinx HDL Coding Hints , and Guide to HDL Coding Styles for Synthesis ).

In practice, we generally don’t see this difference because many synthesis software packages, such as the Xilinx XST, try not to infer a priority encoded logic. Though we can use the PRIORITY_EXTRACT constraint of XST to force priority encoder inference, Xilinx strongly suggests that we use this constraint on a signal-by-signal basis; otherwise, the constraint may guide us towards sub-optimal results. For more details see page 79 of the XST user guide .

- Concurrent statements are executed at the same time and there is no significance to the order of these statements. This type of code is quite different from what we have learned in basic computer programming where the lines of code are executed one after the other.

- The selected signal assignment or the "with/select" assignment allows us to implement the functionality of a multiplexer.

- The options of a “with/select” assignment must be mutually exclusive, i.e., one option cannot be used more than once. Moreover, all the possible values of the control_expression must be included in the set of the options.

- For the "when/else" statement, the expressions after the “when” clauses are evaluated successively. As a result, the expressions evaluated earlier has a higher priority compared to the next ones.

- One important difference between the “with/select” and “when/else” assignment can be seen by comparing the conceptual implementation of these two statements. The "when/else" statement has a priority network; however, the “with/select” assignment avoids this chain structure and has a balanced structure.

To see a complete list of my articles, please visit this page .

Featured image used courtesy of Parallella .

Related Content

- Safety in Sensing: Sensor Technology in Smart Cities

- Thermocouple Signal Conditioners and Signal Conditioning Near the Cold Junction

- Test & Measurement in Quantum Computing

- Reducing Distortion in Tape Recordings with Hysteresis in SPICE

- Open RAN – Network Performance in the Lab and in the Field

- Looking for Good Waves: The Importance of Signal Integrity in High-Speed PCB Design

Learn More About:

- programmable logic

Great content. The link to the ISE guide requires password. Can we get that posted again? Thanks!

You May Also Like

Cost Reduction and Efficiency Enhancement: APM32F035 Laboratory Centrifuge Solution

In Partnership with Geehy Semiconductor

Taoglas Introduces the ‘Industry’s First’ Wi-Fi Antenna for an RJ45 Jack

by Jake Hertz

Solid State Battery Material Offers 100x More Energy Density

by Mike Falter

Expert Q&A: Combatting Environmental Pollutants

by NKK Switches

Oscilloscope Measurements to Satisfy Full-Bridge Converter Verification Requirements

by Rohde & Schwarz

Welcome Back

Don't have an AAC account? Create one now .

Forgot your password? Click here .

VHDL Logical Operators and Signal Assignments for Combinational Logic

In this post, we discuss the VHDL logical operators, when-else statements , with-select statements and instantiation . These basic techniques allow us to model simple digital circuits.

In a previous post in this series, we looked at the way we use the VHDL entity, architecture and library keywords. These are important concepts which provide structure to our code and allow us to define the inputs and outputs of a component.

However, we can't do anything more than define inputs and outputs using this technique. In order to model digital circuits in VHDL, we need to take a closer look at the syntax of the language.

There are two main classes of digital circuit we can model in VHDL – combinational and sequential .

Combinational logic is the simplest of the two, consisting primarily of basic logic gates , such as ANDs, ORs and NOTs. When the circuit input changes, the output changes almost immediately (there is a small delay as signals propagate through the circuit).

Sequential circuits use a clock and require storage elements such as flip flops . As a result, changes in the output are synchronised to the circuit clock and are not immediate. We talk more specifically about modelling combinational logic in this post, whilst sequential logic is discussed in the next post.

Combinational Logic

The simplest elements to model in VHDL are the basic logic gates – AND, OR, NOR, NAND, NOT and XOR.

Each of these type of gates has a corresponding operator which implements their functionality. Collectively, these are known as logical operators in VHDL.

To demonstrate this concept, let us consider a simple two input AND gate such as that shown below.

The VHDL code shown below uses one of the logical operators to implement this basic circuit.

Although this code is simple, there are a couple of important concepts to consider. The first of these is the VHDL assignment operator (<=) which must be used for all signals. This is roughly equivalent to the = operator in most other programming languages.

In addition to signals, we can also define variables which we use inside of processes. In this case, we would have to use a different assignment operator (:=).

It is not important to understand variables in any detail to model combinational logic but we talk about them in the post on the VHDL process block .

The type of signal used is another important consideration. We talked about the most basic and common VHDL data types in a previous post.

As they represent some quantity or number, types such as real, time or integer are known as scalar types. We can't use the VHDL logical operators with these types and we most commonly use them with std_logic or std_logic_vectors.

Despite these considerations, this code example demonstrates how simple it is to model basic logic gates.

We can change the functionality of this circuit by replacing the AND operator with one of the other VHDL logical operators.

As an example, the VHDL code below models a three input XOR gate.

The NOT operator is slightly different to the other VHDL logical operators as it only has one input. The code snippet below shows the basic syntax for a NOT gate.

- Mixing VHDL Logical Operators

Combinational logic circuits almost always feature more than one type of gate. As a result of this, VHDL allows us to mix logical operators in order to create models of more complex circuits.

To demonstrate this concept, let’s consider a circuit featuring an AND gate and an OR gate. The circuit diagram below shows this circuit.

The code below shows the implementation of this circuit using VHDL.

This code should be easy to understand as it makes use of the logical operators we have already talked about. However, it is important to use brackets when modelling circuits with multiple logic gates, as shown in the above example. Not only does this ensure that the design works as intended, it also makes the intention of the code easier to understand.

- Reduction Functions

We can also use the logical operators on vector types in order to reduce them to a single bit. This is a useful feature as we can determine when all the bits in a vector are either 1 or 0.

We commonly do this for counters where we may want to know when the count reaches its maximum or minimum value.

The logical reduction functions were only introduced in VHDL-2008. Therefore, we can not use the logical operators to reduce vector types to a single bit when working with earlier standards.

The code snippet below shows the most common use cases for the VHDL reduction functions.

Mulitplexors in VHDL

In addition to logic gates, we often use multiplexors (mux for short) in combinational digital circuits. In VHDL, there are two different concurrent statements which we can use to model a mux.

The VHDL with select statement, also commonly referred to as selected signal assignment, is one of these constructs.

The other method we can use to concurrently model a mux is the VHDL when else statement.

In addition to this, we can also use a case statement to model a mux in VHDL . However, we talk about this in more detail in a later post as this method also requires us to have an understanding of the VHDL process block .

Let's look at the VHDL concurrent statements we can use to model a mux in more detail.

VHDL With Select Statement

When we use the with select statement in a VHDL design, we can assign different values to a signal based on the value of some other signal in our design.

The with select statement is probably the most intuitive way of modelling a mux in VHDL.

The code snippet below shows the basic syntax for the with select statement in VHDL.

When we use the VHDL with select statement, the <mux_out> field is assigned data based on the value of the <address> field.

When the <address> field is equal to <address1> then the <mux_out> signal is assigned to <a>, for example.

We use the the others clause at the end of the statement to capture instance when the address is a value other than those explicitly listed.

We can exclude the others clause if we explicitly list all of the possible input combinations.

- With Select Mux Example

Let’s consider a simple four to one multiplexer to give a practical example of the with select statement. The output Q is set to one of the four inputs (A,B, C or D) depending on the value of the addr input signal.

The circuit diagram below shows this circuit.

This circuit is simple to implement using the VHDL with select statement, as shown in the code snippet below.

VHDL When Else Statements

We use the when statement in VHDL to assign different values to a signal based on boolean expressions .

In this case, we actually write a different expression for each of the values which could be assigned to a signal. When one of these conditions evaluates as true, the signal is assigned the value associated with this condition.

The code snippet below shows the basic syntax for the VHDL when else statement.

When we use the when else statement in VHDL, the boolean expression is written after the when keyword. If this condition evaluates as true, then the <mux_out> field is assigned to the value stated before the relevant when keyword.

For example, if the <address> field in the above example is equal to <address1> then the value of <a> is assigned to <mux_out>.

When this condition evaluates as false, the next condition in the sequence is evaluated.

We use the else keyword to separate the different conditions and assignments in our code.

The final else statement captures the instances when the address is a value other than those explicitly listed. We only use this if we haven't explicitly listed all possible combinations of the <address> field.

- When Else Mux Example

Let’s consider the simple four to one multiplexer again in order to give a practical example of the when else statement in VHDL. The output Q is set to one of the four inputs (A,B, C or D) based on the value of the addr signal. This is exactly the same as the previous example we used for the with select statement.

The VHDL code shown below implements this circuit using the when else statement.

- Comparison of Mux Modelling Techniques in VHDL

When we write VHDL code, the with select and when else statements perform the same function. In addition, we will get the same synthesis results from both statements in almost all cases.

In a purely technical sense, there is no major advantage to using one over the other. The choice of which one to use is often a purely stylistic choice.

When we use the with select statement, we can only use a single signal to determine which data will get assigned.

This is in contrast to the when else statements which can also include logical descriptors.

This means we can often write more succinct VHDL code by using the when else statement. This is especially true when we need to use a logic circuit to drive the address bits.

Let's consider the circuit shown below as an example.

To model this using a using a with select statement in VHDL, we would need to write code which specifically models the AND gate.

We must then include the output of this code in the with select statement which models the multiplexer.

The code snippet below shows this implementation.

Although this code would function as needed, using a when else statement would give us more succinct code. Whilst this will have no impact on the way the device works, it is good practice to write clear code. This help to make the design more maintainable for anyone who has to modify it in the future.

The VHDL code snippet below shows the same circuit implemented with a when else statement.

Instantiating Components in VHDL

Up until this point, we have shown how we can use the VHDL language to describe the behavior of circuits.

However, we can also connect a number of previously defined VHDL entity architecture pairs in order to build a more complex circuit.

This is similar to connecting electronic components in a physical circuit.

There are two methods we can use for this in VHDL – component instantiation and direct entity instantiation .

- VHDL Component Instantiation

When using component instantiation in VHDL, we must define a component before it is used.

We can either do this before the main code, in the same way we would declare a signal, or in a separate package.

VHDL packages are similar to headers or libraries in other programming languages and we discuss these in a later post.

When writing VHDL, we declare a component using the syntax shown below. The component name and the ports must match the names in the original entity.

After declaring our component, we can instantiate it within an architecture using the syntax shown below. The <instance_name> must be unique for every instantiation within an architecture.

In VHDL, we use a port map to connect the ports of our component to signals in our architecture.

The signals which we use in our VHDL port map, such as <signal_name1> in the example above, must be declared before they can be used.

As VHDL is a strongly typed language, the signals we use in the port map must also match the type of the port they connect to.

When we write VHDL code, we may also wish to leave some ports unconnected.

For example, we may have a component which models the behaviour of a JK flip flop . However, we only need to use the inverted output in our design meaning. Therefore, we do not want to connect the non-inverted output to a signal in our architecture.

We can use the open keyword to indicate that we don't make a connection to one of the ports.

However, we can only use the open VHDL keyword for outputs.

If we attempt to leave inputs to our components open, our VHDL compiler will raise an error.

- VHDL Direct Entity Instantiation

The second instantiation technique is known as direct entity instantiation.

Using this method we can directly connect the entity in a new design without declaring a component first.

The code snippet below shows how we use direct entity instantiation in VHDL.

As with the component instantiation technique, <instance_name> must be unique for each instantiation in an architecture.

There are two extra requirements for this type of instantiation. We must explicitly state the name of both the library and the architecture which we want to use. This is shown in the example above by the <library_name> and <architecture_name> labels.

Once the component is instantiated within a VHDL architecture, we use a port map to connect signals to the ports. We use the VHDL port map in the same way for both direct entity and component instantiation.

Which types can not be used with the VHDL logical operators?

Scalar types such as integer and real.

Write the code for a 4 input NAND gate

We can use two different types of statement to model multiplexors in VHDL, what are they?

The with select statement and the when else statement

Write the code for an 8 input multiplexor using both types of statement

Write the code to instantiate a two input AND component using both direct entity and component instantiation. Assume that the AND gate is compiled in the work library and the architecture is named rtl.

Table of Contents

IMAGES

VIDEO

COMMENTS

If the driven values of the multiple drivers are different (e.g. one '1', the other '0') you'll see a resolution of 'X' during VHDL simulation for the overlap. The pullup implies that the default value of the signal net is 'H' when there are no 'active' drivers providing strong values ('1' or '0'). You'd typically 'filter' the 'H' to a '1' by ...

A bidirectional bus is typically implemented by using a tristate buffer. When the tristate buffer output is "Z" you can read from the inout port, when the buffer is driving the line, it acts as an output. In VHDL, this can be implemented by directly instanciating a primitive (e.g. IOBUF for Xilinx device), or by letting your synthesis tool infer tristate buffer by describing logic as described ...

This example implements an 8-bit bus that feeds and receives feedback from bidirectional pins. For more information on using this example in your project, go to: How to use VHDL examples. bidir.vhd (Tri-state bus implementation) LIBRARY ieee; USE ieee.std_logic_1164.ALL; ENTITY bidir IS PORT ( bidir : INOUT STD_LOGIC_VECTOR (7 DOWNTO 0); oe ...

1. The Inside_process and Outside_process versions behave differently. If both designs work, it is mostly out of luck, because in this case Out_signal simply lags half a clock cycle when declared inside the process. Inside_process. Out_signal is assigned when the process triggers, which in this case occurs on rising and falling edges of clk.

The VHDL model of this chip does not include any delays (in simulations all signals change immediately after the clock edge). For system-level simulations, I am building a wrapping entity around ... -- bidirectional signal assignments with delays DBUS_link: for i in DBUS_ext'range generate DBUSi_link: ZeroOhm

To further complicate things, this bi-directional bus is multiplexed with the address bus. On the low part of the device's clock cycle it will alway output the upper 8-bits of a 24-bit address on the data bus. The lower 16 bits are not valid at that time. At the high part of the cycle it will either drive data out or read it in.

1) I would like to handle bi-directional signals. What is an example of VHDL description? What would be the grammatical problem with the following statement? entity test is. port(BP : inout std_logic; DIR : in std_logic; OD : out std_logic) end test; architecture RTL of test is. signal a: std_logic; signal i: std_logic; begin. BD <= a when (dir ...

55. . when-else vs. with-select-when (1) "when-else" should be used when: there is only one condition (and thus, only one else), as in the 2-to-1 MUX. conditions are independent of each other (e.g., they test values of different signals) conditions reflect priority (as in priority encoder); one with the highest priority need to be tested first.

2. When updated. local variable is immediately updated whe. thevariable assignment statement is executed.A signal. ssignment statement updates the signal driver. The new value of the. gn. ent between variables statement and signals3. Variables are cheaper to implement in VHDL simulatio. since the evaluation of.

The outputs include a 2-bit signal (code), which is the binary code of the highest priority request and a 1-bit signal active that indicates if there is an active request. has the highest priority, i.e., when asserted, the other three requests are ignored and the code signal becomes "11". When r(3) is not asserted, the second highest request, r ...

A selected signal assignment will usually result in combinational logic being generated. Assignments to 'Z' will normally generate tri-state drivers. Assignment to 'X' may not be supported. If a signal is conditionally assigned to itself, latches may be inferred. A usable language reference for VHDL that is concise, direct, and easy to ...

Signal Assignment - Delay; 6.12. VHDL Operators; 6.13. Operator Overloading; 6.14. Operator Overloading Function/Package ... inout for a bidirectional and buffer for an output with internal feedback. Typically input signals and only be read from not written to. ... The signal assignments we have talked about so far have been implied processes ...

1. Assignments in VHDL are neighter specified as registered or combinatorial. In VHDL the actual assignment type (the type of RTL logic generated) is just inferred. Registers in VHDL are created explicitly by assigning a signal on a clock edge, though just because a process has a clock it does not mean all signals in that block will be assigned ...

Conditional Signal Assignment or the "When/Else" Statement. The "when/else" statement is another way to describe the concurrent signal assignments similar to those in Examples 1 and 2. Since the syntax of this type of signal assignment is quite descriptive, let's first see the VHDL code of a one-bit 4-to-1 multiplexer using the ...

Conditional signal assignment. Conditional signal assignment is a form of a concurrent signal assignment and plays the same role in architecture as the if then else construct inside processes. A signal is assigned a waveform if the Boolean condition supported after the when keyword is met. Otherwise, the next condition after the else clause is ...

The VHDL code shown below uses one of the logical operators to implement this basic circuit. and_out <= a and b; Although this code is simple, there are a couple of important concepts to consider. The first of these is the VHDL assignment operator (<=) which must be used for all signals.